# MITAC ND118T User Manual V1.0

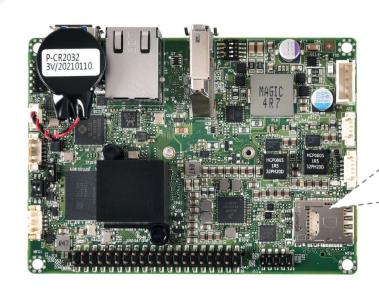

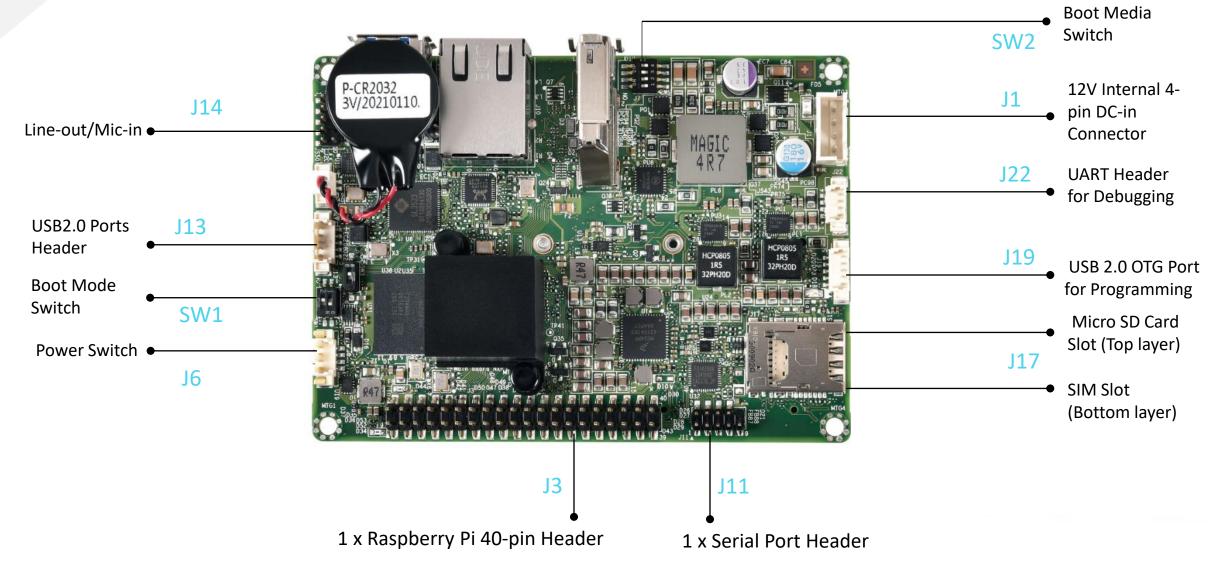

# **MB Placement (Top View)**

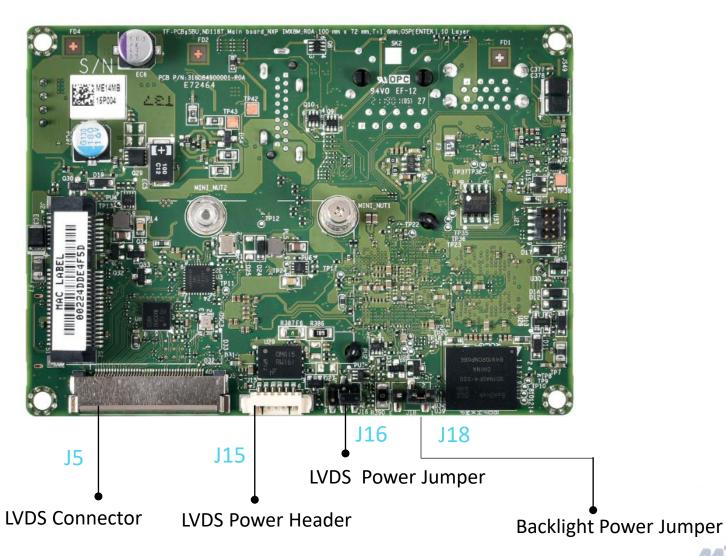

### MB Placement (Bottom View)

### Pin Definition (1/5)

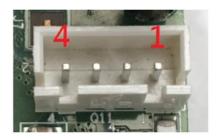

J1

Figure 1: DC IN Connector (J1)

| Pin | Signal |  |

|-----|--------|--|

| 1   | +12V   |  |

| 2   | +12V   |  |

| 3   | Ground |  |

| 4   | Ground |  |

Table 1: DC IN Connector pin-out reference

**Vendor: Joint Tech**

Model: A2501WV-04P146

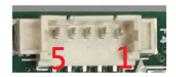

J19

Figure 2: USB 2.0 Header for programming (J19)

| Pin | Signal          |

|-----|-----------------|

| 1   | 5V_USB          |

| 2   | Data (negative) |

| 3   | Data (positive) |

| 4   | Ground          |

| 5   | NC              |

Table 2: 5-pin USB 2.0 header Pin out reference

**Vendor: Molex**

Model: 53398-0571

# Pin Definition (2/5)

J13

Figure 3: Single USB2.0 pin-out for normal use (J13)

| Pin | Signal          |  |

|-----|-----------------|--|

| 1   | SV_USB          |  |

| 2   | Data (negative) |  |

| 3   | Data (positive) |  |

| 4   | Ground          |  |

| 5   | NC              |  |

Table 3: Single USB 2.0 Header

Vendor: Molex Model: 53398-0571

Figure 4: UART pin-out for Debug (J22)

| Pin | Signal            |  |

|-----|-------------------|--|

| 1   | 5V                |  |

| 2   | UART Transmission |  |

| 3   | UART Receive      |  |

| 4   | Ground            |  |

Table 4: UART Header Pin out reference

Vendor: Aces Electronics Model: 85205-04701

### Pin Definition (3/5)

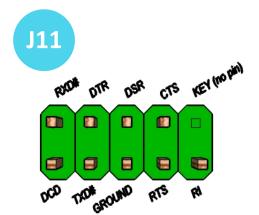

Serial port header pin-out (J11)

| Pin | Signal Name |  |

|-----|-------------|--|

| 1   | DCD         |  |

| 2   | RXD#        |  |

| 3   | TXD#        |  |

| 4   | DTR         |  |

| 5   | GND         |  |

| 6   | DSR         |  |

| 7   | RTS         |  |

| 8   | CTS         |  |

| 9   | RI          |  |

| 10  | Key         |  |

**Vendor: SUPERIOR TECH**

Model: PHDD-SS010G1ABONE-N088

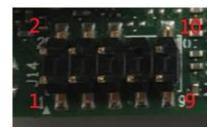

J14

Audio Header (J14)

| Pin | Signal         |  |

|-----|----------------|--|

| 1   | MIC_L          |  |

| 2   | GND            |  |

| 3   | MIC_R          |  |

| 4   | N.C            |  |

| 5   | LINE_OUT_R     |  |

| 6   | N.C            |  |

| 7   | Plug detection |  |

| 8   | Key (no pin)   |  |

| 9   | LINE_OUT_L     |  |

| 10  | N.C            |  |

**Vendor: SUPERIOR TECH**

Model: PHDD-SS010G1ABONE-N098

# Pin Definition (4/5)

J3

Raspberry Pi 40-pin header

| GPIO#  | 2 <sup>nd</sup> Func | Pin# | Pin# | 2 <sup>nd</sup> Func | GPIO#  |

|--------|----------------------|------|------|----------------------|--------|

| N/A    | +3V3                 | 1    | 2    | +5V                  | N/A    |

| GPIO2  | SDA1(I2C)            | 3    | 4    | +5V                  | N/A    |

| GPIO3  | SCL1(I2C)            | 5    | 6    | Ground               | N/A    |

| GPIO4  | GCLK                 | 7    | 8    | UARTO_TXD            | GPIO14 |

| N/A    | Ground               | 9    | 10   | UARTO_RXD            | GPIO15 |

| GPIO17 | GEN0                 | 11   | 12   | GEN1                 | GPIO18 |

| GPIO27 | GEN2                 | 13   | 14   | Ground               | N/A    |

| GPIO22 | GEN3                 | 15   | 16   | GEN4                 | GPIO23 |

| N/A    | +3V3                 | 17   | 18   | GEN5                 | GPIO24 |

| GPIO10 | MOSI(SPI)            | 19   | 20   | Ground               | N/A    |

| GPIO9  | MISO(SPI)            | 21   | 22   | GEN6                 | GPIO25 |

| GPIO11 | SCLK(SPI)            | 23   | 24   | CEO_N(SPI)           | GPI08  |

| N/A    | Ground               | 25   | 26   | CE1_N(SPI)           | GPIO7  |

| EEPROM | ID_SD                | 27   | 28   | ID_SC                | EEPROM |

| GPIO5  | N/A                  | 29   | 30   | Ground               | N/A    |

| GPIO6  | N/A                  | 31   | 32   | un .                 | GPIO12 |

| GPIO13 | N/A                  | 33   | 34   | Ground               | N/A    |

| GPIO19 | N/A                  | 35   | 36   | N/A                  | GPIO16 |

| GPIO26 | N/A                  | 37   | 38   | N/A                  | GPIO20 |

| N/A    | Ground               | 39   | 40   | N/A                  | GPIO21 |

**Vendor: SUPERIOR TECH**

Model: PHED-SS040G1ABONE-B003

Power BTN/RST header (J6)

| Pin | Signal        |  |

|-----|---------------|--|

| 1   | PWRBTN_ON_OFF |  |

| 2   | GND           |  |

| 3   | GND           |  |

| 4   | Reset         |  |

**Vendor: Joint Tech**

Model: A1250WV-S-04PR6NGAG00L

# Pin Definition (5/5)

**J5**

LVDS Connector (J5)

| Pin | Signal           | Description                                |

|-----|------------------|--------------------------------------------|

| 1   | TD0P             | LVDS Channel A diff data output - positive |

| 2   | TD0N             | LVDS Channel A diff data output - negative |

| 3   | TC0P             | LVDS Channel A diff data output - positive |

| 4   | TC0N             | LVDS Channel A diff data output - negative |

| 5   | TB0P             | LVDS Channel A diff data output - positive |

| 6   | TB0N             | LVDS Channel A diff data output - negative |

| 7   | TA0P             | LVDS Channel A diff data output - positive |

| 8   | TAON             | LVDS Channel A diff data output - negative |

| 9   | TD1P             | LVDS Channel B diff data output-positive   |

| 10  | TD1N             | LVDS Channel B diff data output-negative   |

| 11  | TC1P             | LVDS Channel B diff data output-positive   |

| 12  | TC1N             | LVDS Channel B diff data output-negative   |

| 13  | TB1P             | LVDS Channel B diff data output-positive   |

| 14  | TB1N             | LVDS Channel B diff data output-negative   |

| 15  | TA1P             | LVDS Channel B diff data output-positive   |

| 16  | TA1N             | LVDS Channel B diff data output-negative   |

| 17  | GND              | Ground                                     |

| 18  | 3.3V/5V/12V      | Selectable LCD power output                |

| 19  | 3.3V/5V/12V      | Selectable LCD power output                |

| 20  | 3.3V/5V/12V      | Selectable LCD power output                |

| 21  | 3.3V/5V/12V      | Selectable LCD power output                |

| 22  | 3.3V/5V/12V      | Selectable LCD power output                |

| 23  | GND              | Ground                                     |

| 24  | GND              | Ground                                     |

| 25  | GND              | Ground                                     |

| 26  | TCK0P            | LVDS Channel A diff data output - positive |

| 27  | TCK0N            | LVDS Channel A diff data output - negative |

| 28  | GND              | Ground                                     |

| 29  | GND              | Ground                                     |

| 30  | GND              | Ground                                     |

| 31  | DDC_SCL          | LVDS_DDC_SCL                               |

| 32  | DSI_LVDS_BL_EN   |                                            |

| 33  | DSI_LVDS_BL_CTRL |                                            |

| 34  | TCK1P            | LVDS Channel B diff data output - positive |

| 35  | TCK1N            | LVDS Channel B diff data output - negative |

| 36  | BKLT_PWR         | Selectable BKLT power output               |

| 37  | BKLT_PWR         | Selectable BKLT power output               |

| 38  | BKLT_PWR         | Selectable BKLT power output               |

| 39  | BKLT_PWR         | Selectable BKLT power output               |

| 40  | DDC_SDA          | LVDS_DDC_SDA                               |

Aces Electronic Model: 50203-04001-001

### LVDS inverter power header pin-out (J15)

| Pin | Signal Name  | Description           |

|-----|--------------|-----------------------|

| 1   | LVDS_BKTEN_R | Backlight enable      |

| 2   | LVDS_PWM     | Backlight PWM control |

| 3   | 12V/5V       | Inverter power        |

| 4   | 12V/5V       | Inverter power        |

| 5   | GND          | Ground                |

| 6   | GND          | Ground                |

Joint Tech Electronic Model: A1250WRA-S-06P

### **Jumper Setting for Panel**

J18

Backlight power voltage selection header

Pins 1&2: jumper position for 12V

Pins 2&3: jumper position for VCC

| Pin | Signal Name |  |

|-----|-------------|--|

| 1   | 12V         |  |

| 2   | BKLT_PWR    |  |

| 3   | VCC (5V)    |  |

Table 1: Inverter power voltage selection header signals

LVDS Panel power voltage selection header

| Pin | Signal Name | Description              |

|-----|-------------|--------------------------|

| 1   | NC          | NC                       |

| 2   | VCC3        | +3.3V                    |

| 3   | 12V         | 12V                      |

| 4   | PANEL_PWR   | [Out] output panel power |

| 5   | NC          | NC                       |

| 6   | VCC         | +5V                      |

Table 3: LVDS panel power header signals

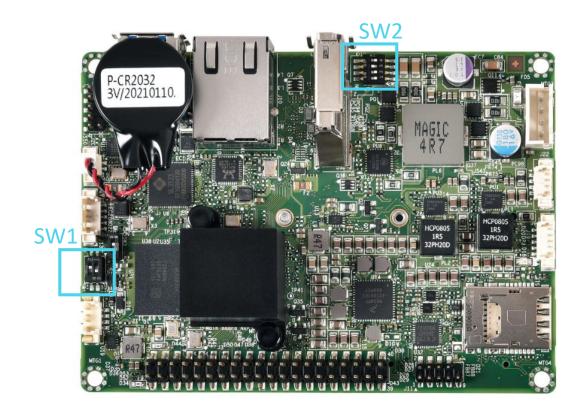

# **DIP Switch Setting**

| SW1 (Boot Mode DIP) |      |                      |  |  |

|---------------------|------|----------------------|--|--|

| DIP1                | DIP2 | Boot Source          |  |  |

| OFF                 | ON   | Serial Download Mode |  |  |

| ON                  | OFF  | Internal Boot Mode   |  |  |

| SW2 (Boot Media DIP) |      |      |      |                          |  |

|----------------------|------|------|------|--------------------------|--|

| DIP1                 | DIP2 | DIP3 | DIP4 | Boot Media Configuration |  |

| OFF                  | OFF  | ON   | OFF  | eMMC                     |  |

| ON                   | ON   | OFF  | OFF  | microSD                  |  |

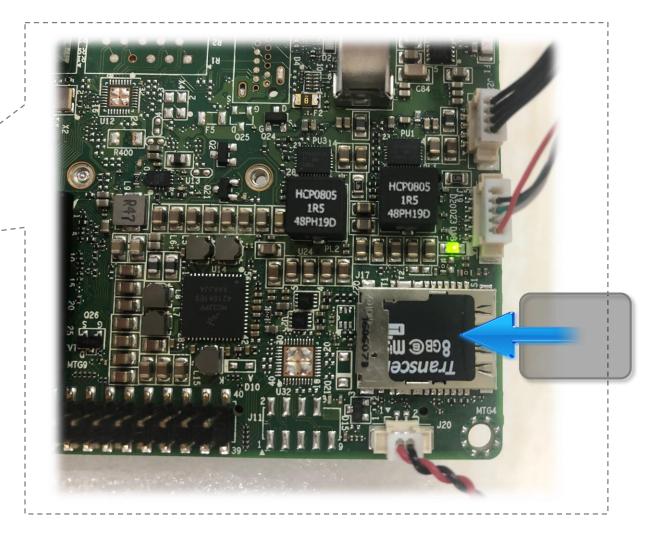

### How to insert the Micro SD card